## SmScO 3 thin films as an alternative gate dielectric

E. Durğun Özben, J. M. J. Lopes, M. Roeckerath, St. Lenk, B. Holländer, Y. Jia, D. G. Schlom, J. Schubert, and S. Mantl

Citation: Applied Physics Letters **93**, 052902 (2008); doi: 10.1063/1.2968660 View online: http://dx.doi.org/10.1063/1.2968660 View Table of Contents: http://scitation.aip.org/content/aip/journal/apl/93/5?ver=pdfcov Published by the AIP Publishing

## Articles you may be interested in

Amorphous lanthanum lutetium oxide thin films as an alternative high- κ gate dielectric Appl. Phys. Lett. **89**, 222902 (2006); 10.1063/1.2393156

Gadolinium scandate thin films as an alternative gate dielectric prepared by electron beam evaporation Appl. Phys. Lett. **88**, 172901 (2006); 10.1063/1.2198103

Structure and dielectric properties of amorphous LaAIO 3 and LaAIO x N y films as alternative gate dielectric materials J. Appl. Phys. **94**, 1229 (2003); 10.1063/1.1586976

Epitaxial growth of yttrium-stabilized HfO 2 high-k gate dielectric thin films on Si J. Appl. Phys. **94**, 912 (2003); 10.1063/1.1585116

Effect of growth temperature on the properties of evaporated tantalum pentoxide thin films on silicon deposited using oxygen radicals J. Appl. Phys. **84**, 1632 (1998); 10.1063/1.368256

This article is copyrighted as indicated in the article. Reuse of AIP content is subject to the terms at: http://scitation.aip.org/termsconditions. Downloaded to IP: 128.84.143.26 On: Fri, 08 May 2015 18:32:37

## SmScO<sub>3</sub> thin films as an alternative gate dielectric

E. Durğun Özben,<sup>1,a)</sup> J. M. J. Lopes,<sup>1</sup> M. Roeckerath,<sup>1</sup> St. Lenk,<sup>1</sup> B. Holländer,<sup>1</sup> Y. Jia,<sup>2</sup> D. G. Schlom,<sup>2</sup> J. Schubert,<sup>1</sup> and S. Mantl<sup>1</sup>

<sup>1</sup>Institute for Bio- and Nanosystems (IBN1-IT), Research Center Juelich, D-52425 Juelich, Germany <sup>2</sup>Department of Materials Science and Engineering, The Pennsylvania State University, University Park, Pennsylvania 16802-5005, USA

(Received 4 June 2008; accepted 17 July 2008; published online 5 August 2008)

Samarium scandate thin films deposited on (100) Si have been investigated structurally and electrically. Rutherford backscattering spectrometry and transmission electron microscopy results show that the films are stoichiometric, amorphous, and smooth. X-ray diffraction analysis indicates that SmScO<sub>3</sub> starts to crystallize at 900 °C. Capacitance and leakage current measurements reveal *C-V* curves with negligible hysteresis, a dielectric constant around 29 for 6 nm thick films, low leakage current densities in the range of  $10^{-7}$  A/cm<sup>2</sup>, an effective oxide charge density of ~5  $\times 10^{11}$  (cm<sup>-2</sup>), and an interface trap density of  $4.5 \times 10^{11}$  (eV cm<sup>2</sup>)<sup>-1</sup>. © 2008 American Institute of Physics. [DOI: 10.1063/1.2968660]

The dielectric  $SiO_2$  has been the key to the tremendous improvements in Si-based metal-oxide-semiconductor (MOS) device performance over the past four decades. It has, however, reached its limit in terms of scaling since it exhibits a leakage current density higher than 1  $A/cm^2$  and does not retain its intrinsic physical properties at thicknesses below 1.5 nm.<sup>1,2</sup> In order to overcome these problems and keep Moore's law ongoing, the use of higher dielectric constant ( $\kappa$ ) gate oxides has been suggested. These high- $\kappa$  materials must satisfy numerous requirements including high  $\kappa$ , large band gap and band offsets, low leakage current density, low interface trap density, high breakdown strength, acceptable reliability, and additionally thermal stability in contact with silicon. Recently, Intel reported the first 45 nm microprocessors using a hafnium-based gate oxide together with an appropriate metal gate material. The transistors in these microprocessors exhibit an order of magnitude lower gate leakage than transistors with an SiO<sub>2</sub> gate dielectric.<sup>3</sup> Tomida et al. observed that  $Hf_{(1-x)}Si_xO_2$  shows different  $\kappa$  values depending on the crystallization phase.<sup>4</sup> They observed that amorphous  $Hf_{(1-r)}Si_rO_2$  shows a  $\kappa$  value around 20; however, for monoclinic phase, the  $\kappa$  value is 15 and as they increased the temperature and changed the crystallization phase from monoclinic to tetragonal the  $\kappa$  value increased to 27. Moreover, Böscke *et al.*<sup>5</sup> and Migita *et al.*<sup>6</sup> obtained a  $\kappa$ of 36 and an even higher  $\kappa$  value for tetragonal and cubic HfO<sub>2</sub>, respectively. However the  $\kappa$  of amorphous hafniumbased oxides varies between 10 and 20.7,8 In contrast, rare earth (RE) scandates (REScO<sub>3</sub>, RE=Gd, Dy, La) show higher  $\kappa$  and, therefore, have attracted significant attention for high- $\kappa$  applications.<sup>9-13</sup> The amorphous RE scandates have  $\kappa$  between 20 and 30 and the crystalline phases have  $\kappa$ over 30.<sup>12</sup> Christen et al. observed band gaps higher than 5.5 eV for these REScO<sub>3</sub> oxides and varying crystallization temperatures depending on the RE atomic number and the Goldschmidt tolerance factor.<sup>12</sup> According to their results, the crystallization temperature of SmScO3 (750 °C) lies intermediate between those of LaScO<sub>3</sub> (650 °C) and GdScO<sub>3</sub> (800 °C), however, among them it has the highest  $\kappa$  when crystallized. So far there are no experimental results about the application of amorphous SmScO<sub>3</sub> as a gate dielectric. The aim of this paper is therefore to establish the properties of amorphous SmScO<sub>3</sub> thin films concerning the above-mentioned requirements for high- $\kappa$  materials.

SmScO<sub>3</sub> films with thicknesses ranging from 6 to 62 nm were deposited by pulsed-laser deposition (PLD) using a stoichiometric ceramic target. RCA cleaned *p*-type (100) Si wafers were used as substrates. Prior to film deposition the wafers were heated to 400 °C and the deposition was carried out in  $2 \times 10^{-3}$  mbar O<sub>2</sub> with a fluence of 2.5 J/cm<sup>2</sup> and a pulse rate of 10 Hz from a 248 nm (KrF) excimer laser. After the deposition, the structure, stoichiometry, and thermal stability of the films were investigated using Rutherford back-scattering spectrometry (RBS), transmission electron microscopy (TEM), and x-ray diffraction (XRD).

For electrical characterization, MOS capacitors were fabricated. 70 nm thick Pt top contacts were deposited by electron beam evaporation through a shadow mask with areas between  $2 \times 10^{-4}$  and  $11.5 \times 10^{-4}$  cm<sup>2</sup>. An Ohmic backside contact was realized by depositing 120 nm Al. Finally, the samples were annealed in forming gas (90% N<sub>2</sub> + 10% H<sub>2</sub>) for 13 min at 450 °C to improve their electrical properties.

High frequency *C-V* measurements were carried out using an impedance analyzer (HP 4192A) at 100 kHz. The work function of the metal gate and the effective charge density in the oxide were obtained from the high frequency *C-V* results. The density of the interface trap states ( $D_{it}$ ) was calculated using Terman's method.<sup>14</sup> Finally, leakage current measurements were performed using a semiconductor parameter analyzer (HP 4155B).

The stoichiometry and thickness of the films were determined by RBS. Simulation of the RBS data using the rump program<sup>15</sup> reveals that the films have the desired stoichiometry with a ratio of Sm:Sc:O=1:1:3.

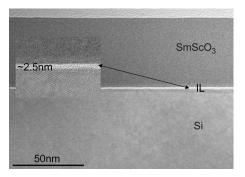

A cross-sectional TEM image of a 49 nm thick  $SmScO_3$ film on Si (100) (Fig. 1) shows an amorphous and smooth film on Si. The figure also indicates the existence of an interfacial layer between the silicon and the high- $\kappa$  dielectric

<sup>&</sup>lt;sup>a)</sup>Electronic mail: eylemdurgun@gmail.com.

FIG. 1. Cross-sectional TEM micrograph of a 49 nm thick SmScO<sub>3</sub> film deposited on (100) Si. The inset shows a close-up of the interlayer, which has a thickness of about 2.5 nm.

with a thickness of 2.5 nm. The growth of the interfacial layer is probably related to the oxidation of the silicon surface during PLD growth.

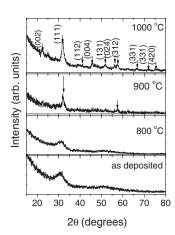

In order to study the thermal stability of the SmScO<sub>3</sub> grown at 400 °C, rapid thermal annealing in ultrapure N<sub>2</sub> was performed at atmospheric pressure and different temperatures ranging from 700 to 1100 °C for 10 s. Figure 2 shows the XRD patterns of a 22 nm thick SmScO<sub>3</sub> film for different annealing temperatures. It is apparent that the asdeposited film is amorphous, in agreement with the TEM results. The film remains amorphous up to 800 °C and the crystallization of the orthorhombic SmScO<sub>3</sub> phase starts at 900 °C, as indicated by the arrows identifying SmScO<sub>3</sub> reflections. The value for the onset of crystallization is higher than that for  $HfO_2$  (Ref. 16) and comparable to Hf silicates.<sup>17</sup> It is, however, lower than for  $DyScO_3$  and  $GdScO_3$ .<sup>10</sup>

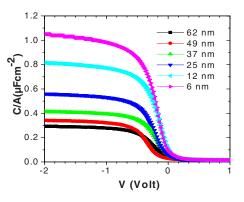

Figure 3 shows the capacitance normalized to the gate area versus gate voltage for SmScO<sub>3</sub> films with different thicknesses. The C-V curves are smooth and free of humps. Double sweep measurements from inversion to accumulation and back were carried out at a frequency of 100 kHz with a 3 s hold time for each measuring point. Negligible counter clockwise hysteresis indicates that these samples contain a low density of positive trap charges,  $Q_{\rm ot}$ , in the range of ~10<sup>10</sup> cm<sup>-2</sup>, as estimated from the simple formula,  $Q_{\rm ot} = (C_{\rm ox}/q)\Delta V_{\rm FB}$ ,<sup>18</sup> where  $C_{\rm ox}$  is the accumulation capacitance normalized to the gate area, q is the electron charge, and  $\Delta V_{\rm FB}$  is the voltage shift from the reverse bias measurement to the forward one.

FIG. 2. XRD patterns of a  $\sim$ 22 nm thick, as deposited SmScO<sub>3</sub> film grown on (100) Si, together with those after annealing at different temperatures in This articles Nace as indicated in the article. Reuse of AIP content is subjects the terms at: http://scitation.aip.org/termsconditions. Downloaded to IP:

FIG. 3. (Color online) Capacitance normalized to the gate area vs gate voltage of Pt/SmScO<sub>3</sub>/Si MOS capacitors with different oxide thicknesses.

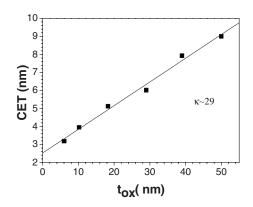

Using the curves shown in Fig. 3, the capacitance equivalent thickness (CET) was extracted from the capacitance in the accumulation region  $C_{\rm acc}$  as CET = $A\varepsilon_0\kappa_{\rm SiO_2}/C_{\rm acc}$ , where A is the gate area,  $\varepsilon_0$  is the permittivity of vacuum and  $\kappa_{SiO_2}$  the dielectric constant of SiO<sub>2</sub>. Figure 4 shows a plot of the CET versus oxide thickness  $t_{ox}$ . From the slope of the linear fit, it is possible to extract the dielectric constant of the films disregarding the contribution of the interfacial layer. The  $\kappa$  thus obtained for amorphous SmScO<sub>3</sub> is  $\sim$ 29. The intercept of the line with the CET axis represents the electrical thickness of the lower- $\kappa$  interfacial layer, which is found to be 2.5 nm. This value is in agreement with the physical interfacial layer thickness observed by TEM indicating that this layer has a  $\kappa$  comparable to SiO<sub>2</sub> and thus likely is SiO<sub>2</sub>.

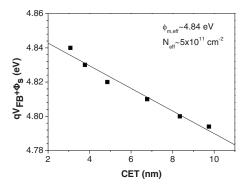

The flatband voltage  $(V_{\rm FB})$  of the samples has been extracted from the comparison between the ideal C-V curves and experimental ones obtained from the capacitors exposed to forming gas annealing at 450 °C. The sample with a 6 nm thick  $SmScO_3$  oxide layer has a -0.1 V flatband shift and as the thickness of the oxide layer increases the flatband voltage shifts to more negative voltages. In order to evaluate the effective oxide charge density  $(N_{eff})$  and the effective work function of the Pt metal gate ( $\Phi_{m,eff}$ ),  $V_{FB}+\Phi_s$  versus CET was plotted in Fig. 5, where  $\Phi_s$  is the work function of the silicon.  $V_{\rm FB}$  can be expressed as<sup>19</sup>

$$V_{\rm FB} = \Phi_{m,\rm eff} \Phi_s - q N_{\rm eff} CET / \varepsilon_{\rm o} \kappa_{\rm SiO_2},$$

where N<sub>eff</sub> does not change with the oxide layer thickness.

FIG. 4. Calculated CET vs  $t_{ox}$  of Pt/SmScO<sub>3</sub>/Si MOS capacitors. The slope of the best-fit line indicates that  $\kappa \sim 29$  and its intercept at 2.5 nm on the CET axis corresponds to the electrical thickness of the lower- $\kappa$  interfacial

FIG. 5.  $V_{FB}+\Phi_s$  vs CET. The intercept of the best-fit line on the  $V_{FB}+\Phi_s$  axis gives  $\Phi_{m,eff}$  and the slope  $N_{eff}$ .

From the intercept of the  $V_{\rm FB} + \Phi_s$  axis,  $\Phi_{m,\rm eff}$  was found to be 4.84 eV. This value satisfies the work function requirement for a *p*-type MOS field-effect transistor. From the slope of the curve N<sub>eff</sub> was evaluated to be  $5 \times 10^{11}$  cm<sup>-2</sup>. Such a low charge density indicates a low concentration of defects in the oxide layer.

Another important issue for MOS capacitors is the quality of the high  $\kappa$ /Si interface. To evaluate the quality of the Si/SmScO<sub>3</sub> interface after forming gas annealing,  $D_{it}$  levels were calculated using Terman's method. The values are  $\sim 4.5 \times 10^{11}$  (eV cm<sup>2</sup>)<sup>-1</sup> and do not show a clear dependence on the oxide thickness, as expected. Finally, the leakage current density of the samples was measured. For the sample with a 6 nm thick SmScO<sub>3</sub> it is in the range of  $10^{-7}$  A/cm<sup>2</sup> and, for thicker films, it is even below the detection limit of the measurement system for the contact size used.

We have investigated the thermal stability and electrical properties of SmScO<sub>3</sub> thin films and their interface to Si (100). The films remain amorphous on Si up to 800 °C and start to crystallize at 900 °C. The results indicate low oxide charge and interface trap charge densities in the range of  $5 \times 10^{11}$  cm<sup>-2</sup> and  $4.5 \times 10^{11}$  (eV cm<sup>2</sup>)<sup>-1</sup>, respectively. Very smooth *C*-*V* curves with negligible hysteresis were recorded and a  $\kappa$  value of ~29 was extracted from the electrical mea-

surements. The films reveal low leakage current densities in the range of  $10^{-7}$  A/cm<sup>2</sup> for 6 nm thick film. It can be concluded that amorphous SmScO<sub>3</sub> shows promising properties as an alternative high- $\kappa$  gate dielectric, which might allow it to be used in future integrated circuits.

<sup>1</sup>X. Gou and T. P. Ma, IEEE Electron Device Lett. 19, 207 (1998).

- <sup>2</sup>D. A. Muller, T. Sorsch, S. Moccio, F. H. Baumann, K. Evans-Lutterodt, and G. Timp, Nature (London) **399**, 758 (1999).

- <sup>3</sup>M. T. Bohr, R. S. Chau, T. Ghani, and K. Mistry, IEEE Spectrum 44, 29 (2007).

- <sup>4</sup>K. Tomida, K. Kita, and A. Toriumi, Appl. Phys. Lett. **89**, 142902 (2006).

<sup>5</sup>T. S. Böscke, S. Govindarajan, C. Fachmann, J. Heitmann, A. Avellán, U.

- Schröder, S. Kudelka, P. D. Kirsch, C. Krug, P. Y. Hung, S. C. Song, B. S. Ju, J. Price, G. Pant, B. E. Gnade, W. Krautschneider, B.-H. Lee, and R. Jammy, Proceedings of the IEDM, 2006 (unpublished).

- <sup>6</sup>S. Migita, Y. Watanabe, H. Ota, H. Ito, Y. Kamimuta, T. Nabatame, and A. Toriumi, Proceedings of the VLSI, 2008 (unpublished).

- <sup>'</sup>R. Essary, K. Ramani, V. Craciun, and R. K. Singh, Appl. Phys. Lett. 88, 182902 (2006).

- <sup>8</sup>J. L. Roberts, P. A. Marshall, A. C. Jones, P. R. Chalker, J. F. Bickley, P. A. Williams, S. Taylor, L. M. Smith, G. W. Critchlow, M. Schumacher, and J. Lindner, J. Mater. Chem. **14**, 391 (2004).

- <sup>9</sup>J. M. J. Lopes, M. Roeckerath, T. Heeg, U. Littmark, J. Schubert, S. Mantl, Y. Jia, and D. G. Schlom, Microelectron. Eng. **84**, 1890 (2007).

- <sup>10</sup>M. Wagner, T. Heeg, J. Schubert, C. Zhao, O. Richard, M. Caymax, V. V. Afanas'ev, and S. Mantl, Solid-State Electron. **50**, 58 (2006).

- <sup>11</sup>M. Wagner, T. Heeg, J. Schubert, St. Lenk, S. Mantl, C. Zhao, M. Caymax, and S. De Gendt, Appl. Phys. Lett. 88, 172901 (2006).

- <sup>12</sup>H. M. Christen, G. E. Jellison, Jr., I. Ohkubo, S. Huang, M. E. Reeves, E. Cicerrella, J. L. Freeouf, Y. Jia, and D. G. Schlom, Appl. Phys. Lett. 88, 262906 (2006).

- <sup>13</sup>C. Zhao, T. Witters, B. Brijs, H. Bender, O. Richard, M. Caymax, T. Heeg, J. Schubert, V. V. Afanas'ev, A. Stesmans, and D. G. Schlom, Appl. Phys. Lett. 86, 132903 (2005).

- <sup>14</sup>E. H. Nicollian and J. R. Brews, *MOS Technology* (Wiley, New York, 1982).

- <sup>15</sup>L. R. Doolittle, Nucl. Instrum. Methods Phys. Res. B 33, 891 (1988).

- <sup>16</sup>E. P. Gusev, C. Cabral, Jr., M. Copel, C. D'Emic, and M. Gribelyuk, Microelectron. Eng. **69**, 145 (2003).

- <sup>17</sup>J. Kim and K. Yong, J. Cryst. Growth **263**, 442 (2004).

- <sup>18</sup>H. Bang and J. H. Cho, J. Korean Phys. Soc. **42**, 316 (2003).

- <sup>19</sup>M. Tapajna, K. Husekova, D. Machajdik, A. P. Kobzev, T. Schram, R. Luptak, L. Harmatha, and K. Frohlich, Microelectron. Eng. 83, 2412 (2006).